Product Summary

The IS61LV256-12JI is a very high-speed, low power, 32768-word by 8-bit static RAM. The IS61LV256-12JI is fabricated using ICSIs high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields access times as fast as 8ns maximum. When CE is high, the IS61LV256-12JI assumes a standby mode at which the power dissipation is reduced to 50μW with CMOS input levels. Easy memory expansion is provided by using an active low chip enable. The active low write enable controls both writing and reading of the memory. The IS61LV256-12JI is available in the JED EC stanard 28-pin, 300mil SOJ and the 8*13.4mm TSOP-1 package.

Parametrics

IS61LV256-12JI absolute maximum ratings: (1)VCC, power supply voltage relative to GND: -0.5 to 4.6V; (2)VTERM, terminal voltage with respect to GND: -0.5 to 4.6V; (3)TBIAS, temperature under bias: -10 to 85℃; (4)TSTG, storage temperature: -65 to 150℃; (5)PD, power dissipation: 1W; (6)IOUT, DC output current: ±20mA.

Features

IS61LV256-12JI features: (1)high-speed access times: 8, 10, 12, 15, 20ns; (2)automatic power-down when chip is deselected; (3)CMOS low power operation: 345mW max operating; 7mW max CMOS standby; (4)TTL compatible interface levels; (5)single 3.3V power supply; (6)fully static operation: no clock or refresh required; (7)three-state outputs.

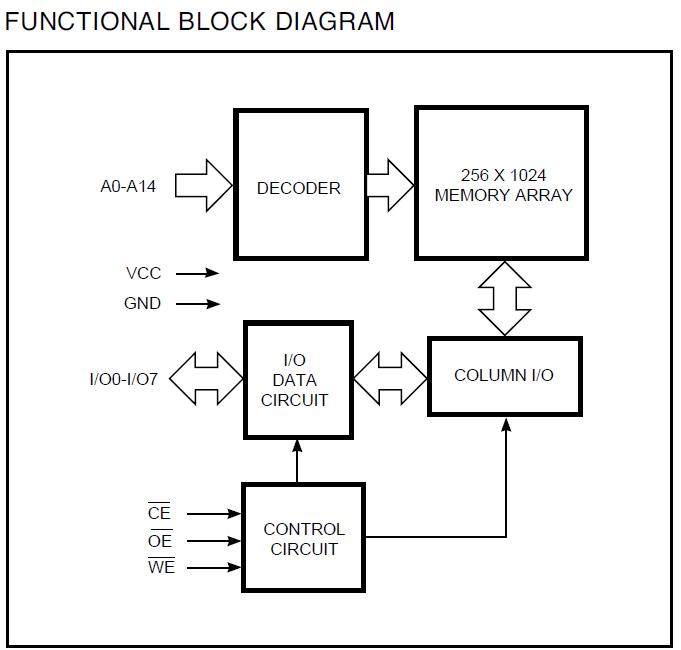

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

IS61LV256-12JI |

ISSI |

SRAM 256K 32Kx8 12ns 3.3v |

Data Sheet |

Negotiable |

|

||||

|

IS61LV256-12JI-TR |

ISSI |

SRAM 256K 32Kx8 12ns 3.3v |

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)